# **CENICS 2016**

The Ninth International Conference on Advances in Circuits, Electronics and Micro-electronics

ISBN: 978-1-61208-496-1

July 24 - 28, 2016

Nice, France

## **CENICS 2016 Editors**

Steffen G. Scholz, Karlsruhe Institute of Technology, Germany

Adrien Brunet, Karlsruhe Institute of Technology, Germany

Leo Schranzhofer, Profactor GmbH, Austria

## **CENICS 2016**

## Forward

The Ninth International Conference on Advances in Circuits, Electronics and Microelectronics (CENICS 2016), held between July 24-28, 2016 in Nice, France, continued a series of events initiated in 2008, capturing the advances on special circuits, electronics, and microelectronics on both theory and practice, from fabrication to applications using these special circuits and systems. The topics covered fundamentals of design and implementation, techniques for deployment in various applications, and advances in signal processing.

Innovations in special circuits, electronics and micro-electronics are the key support for a large spectrum of applications. The conference is focusing on several complementary aspects and targets the advances in each on it: signal processing and electronics for high speed processing, micro- and nano-electronics, special electronics for implantable and wearable devices, sensor related electronics focusing on low energy consumption, and special applications domains of telemedicine and ehealth, bio-systems, navigation systems, automotive systems, home-oriented electronics, bio-systems, etc. These applications led to special design and implementation techniques, reconfigurable and self-reconfigurable devices, and require particular methodologies to be integrated on already existing Internet-based communications and applications. Special care is required for particular devices intended to work directly with human body (implantable, wearable, ehealth), or in a human-close environment (telemedicine, house-oriented, navigation, automotive). The mini-size required by such devices confronted the scientists with special signal processing requirements

The conference had the following tracks:

- Design, models and language

- Application-driven Advances in Additive Manufacturing Technologies

- Special circuits

We take here the opportunity to warmly thank all the members of the CENICS 2016 technical program committee, as well as all the reviewers. The creation of such a high quality conference program would not have been possible without their involvement. We also kindly thank all the authors that dedicated much of their time and effort to contribute to CENICS 2016. We truly believe that, thanks to all these efforts, the final conference program consisted of top quality contributions.

Also, this event could not have been a reality without the support of many individuals, organizations and sponsors. We also gratefully thank the members of the CENICS 2016 organizing committee for their help in handling the logistics and for their work that made this professional meeting a success.

We hope CENICS 2016 was a successful international forum for the exchange of ideas and results between academia and industry and to promote further progress in the field of circuits, electronics and microelectronics. We also hope that Nice, France provided a pleasant

environment during the conference and everyone saved some time enjoy the beautiful French Riviera.

## **CENICS 2016 Advisory Committee**

Vladimir Privman, Clarkson University - Potsdam, USA Sergey Y. Yurish, Technical University of Catalonia (UPC-Barcelona), Spain Martin Horauer, University of Applied Sciences Technikum Wien, Austria Adrian Muscat, University of Malta, Malta

## **CENICS 2016 Research/Industry Chairs**

Ravi M. Yadahalli, S G Balekundri Institute of Technology, Belagavi, Karnataka, India

## **CENICS 2016 Industry Liaison Chairs**

Falk Salewski, Muenster University of Applied Sciences, Germany

## **CENICS 2016 Special Area Chairs**

## **Application-oriented**

Josu Etxaniz Marañon, University of the Basque Country / Universidad del País Vasco / Euskal Herriko Unibertsitatea - Bilbao, Spain

## Sensors

Yulong Zhao, Xi'an Jiaotong University, China

## **Consumer electronics**

Sandra Sendra Compte, University of Granada, Spain

## **CENICS 2016**

## Committee

### **CENICS Advisory Committee**

Vladimir Privman, Clarkson University - Potsdam, USA Sergey Y. Yurish, Technical University of Catalonia (UPC-Barcelona), Spain Martin Horauer, University of Applied Sciences Technikum Wien, Austria Adrian Muscat, University of Malta, Malta

### **CENICS 2016 Research/Industry Chairs**

Ravi M. Yadahalli, S G Balekundri Institute of Technology, Belagavi, Karnataka, India

### **CENICS 2016 Industry Liaison Chairs**

Falk Salewski, Muenster University of Applied Sciences, Germany

### **CENICS 2016 Special Area Chairs**

### **Application-oriented**

Josu Etxaniz Marañon, University of the Basque Country / Universidad del País Vasco / Euskal Herriko Unibertsitatea - Bilbao, Spain

### Sensors

Yulong Zhao, Xi'an Jiaotong University, China

### **Consumer electronics**

Sandra Sendra Compte, University of Granada, Spain

## **CENICS 2016 Technical Program Committee**

Amr Abdel-Dayem, Laurentian University, Canada Amir Shah Abdul Aziz, TM Research & Development, Malaysia Adel Al-Jumaily, University of Technology, Sydney Said Al-Sarawi, The University of Adelaide, Australia Mohammad Amin Amiri, Iran University of Science and Technology, Iran Jose Hugo Barron Zambrano, Autonomous University of Tamaulipas, Mexico Henri Basson, University of Lille North of France (Littoral), France Lotfi Bendaouia, ETIS-ENSEA, France Manuel José Cabral dos Santos Reis, University of Trás-os-Montes e Alto Douro, Portugal Javier Calpe, University of Valencia, Spain James M. Conrad, University of North Carolina at Charlotte, USA Jose Carlos Meireles Monteiro Metrolho, Polytechnic Institute of Castelo Branco, Portugal David Cordeau, CNRS-XLIM, UMR 7252, University of Poitiers, France Marc Daumas, Université de Perpignan, France Javier Diaz-Carmona, Technological Institute of Celaya, Mexico Gordana Jovanovic Dolecek, Institute INAOE - Puebla, Mexico Rolf Drechsler, University of Bremen, Germany Ykhlef Fayçal, Centre de Développement des Technologies Avancées, Algeria Sérgio Adriano Fernandes Lopes, Universidade do Minho, Portugal Francisco V. Fernández, IMSE, CSIC and University of Sevilla, Spain Patrick Girard, LIRMM, France Luis Gomes, Universidade Nova de Lisboa, Portugal Petr Hanáček, Brno University of Technology, Czech Republic Houcine Hassan, Polytechnic University of Valencia, Spain Martin Horauer, University of Applied Sciences Technikum Wien, Austria Chun-Hsi Huang, University of Connecticut, U.S.A. Michael Huebner, Ruhr-University of Bochum, Germany Wen-Jyi Hwang, National Taiwan Normal University, Taiwan Emilio Jiménez Macías, University of La Rioja, Spain Anastasia N. Kastania, Athens University of Economics and Business, Greece Kenneth Blair Kent, University of New Brunswick, Canada Krzysztof Kepa, GE Global Research, USA Eric Kerherve, University of Bordeaux, France Joo-Young Kim, Microsoft, USA Kenji Kise, Tokyo Institute of Technology, Japan Israel Koren, University of Massachusetts at Amherst, USA Tomas Krilavicius, Vytautas Magnus University - Kaunas & Baltic Institute of Advanced Technologies -Vilnius, Lithuania Junghee Lee, University of Texas at San Antonio, USA Kevin Lee, Murdoch University, Australia Hongen Liao, Tsinghua University, China Diego Liberati, National Research Council of Italy, Italy Yo-Sheng Lin, National Chi Nan University, Taiwan Alie Eldin Mady, University College Cork (UCC) - Cork, Ireland Cesare Malagu', University of Ferrara and Istituto di acustica e sensoristica Orso Maria Corbino CNR-IDASC, Italy José Carlos Metrôlho, Instituto Politécnico de Castelo Branco, Portugal Harris Michail, Cyprus University of Technology, Cyprus Yoshikazu Miyanaga, Hokkaido University, Japan Bartolomeo Montrucchio, Politecnico di Torino, Italy Adrian Muscat, University of Malta, Malta Shinobu Nagayama, Hiroshima City University, Japan Arnaldo Oliveira, Universidade de Aveiro, Portugal Adam Pawlak, Silesian University of Technology - Gliwice, Poland George Perry, University of Texas at San Antonio, USA Angkoon Phinyomark, Prince of Songkla University, Thailand Eduardo Correia Pinheiro, Instituto de Telecomunicações - Lisboa, Portugal Katalin Popovici, MathWorks, USA Adam Postula, University of Queensland, Australia Anton Satria Prabuwono, Universiti Kebangsaan Malaysia, Malaysia

Vladimir Privman, Clarkson University - Potsdam, USA Càndid Reig, University of Valencia, Spain Marcos Rodrigues, Sheffield Hallam University, U.K. Julio Sahuquillo, Universitat Politècnica de València, Spain Falk Salewski, Muenster University of Applied Sciences, Germany Sergei Sawitzki, FH Wedel (University of Applied Sciences), Germany Sandra Sendra Compte, University of Granada, Spain Marc Sevaux, Université de Bretagne-Sud, France Arvind K. Srivastava, NanoSonix Inc., USA Ephraim Suhir, University of California – Santa Cruz, USA Ivo Stachiv, National Chung-Cheng University / Institute of Physics - Czech Academy of Sciences, Taiwan / & Czech Republic João Manuel R. S. Tavares, Universidade do Porto, Portugal Felix Toran, European Space Agency, Germany Francisco Torrens, Institut Universitari de Ciencia Molecular / Universitat de Valencia, Spain Carlos M. Travieso-González, University of Las Palmas de Gran Canaria, Spain Miroslav Velev, Aries Design Automation, USA Manuela Vieira, UNINOVA/ISEL, Portugal Thomas Webster, Northeastern University, USA Chin-Long Wey, National Central University, Taiwan Robert Wille, Johannes Kepler University Linz, Austria Ravi M. Yadahalli, S G Balekundri Institute of Technology, Belagavi, Karnataka, India Sergey Y. Yurish, IFSA, Spain David Zammit-Mangion, University of Malta – Msida, Malta

## **Copyright Information**

For your reference, this is the text governing the copyright release for material published by IARIA.

The copyright release is a transfer of publication rights, which allows IARIA and its partners to drive the dissemination of the published material. This allows IARIA to give articles increased visibility via distribution, inclusion in libraries, and arrangements for submission to indexes.

I, the undersigned, declare that the article is original, and that I represent the authors of this article in the copyright release matters. If this work has been done as work-for-hire, I have obtained all necessary clearances to execute a copyright release. I hereby irrevocably transfer exclusive copyright for this material to IARIA. I give IARIA permission or reproduce the work in any media format such as, but not limited to, print, digital, or electronic. I give IARIA permission to distribute the materials without restriction to any institutions or individuals. I give IARIA permission to submit the work for inclusion in article repositories as IARIA sees fit.

I, the undersigned, declare that to the best of my knowledge, the article is does not contain libelous or otherwise unlawful contents or invading the right of privacy or infringing on a proprietary right.

Following the copyright release, any circulated version of the article must bear the copyright notice and any header and footer information that IARIA applies to the published article.

IARIA grants royalty-free permission to the authors to disseminate the work, under the above provisions, for any academic, commercial, or industrial use. IARIA grants royalty-free permission to any individuals or institutions to make the article available electronically, online, or in print.

IARIA acknowledges that rights to any algorithm, process, procedure, apparatus, or articles of manufacture remain with the authors and their employers.

I, the undersigned, understand that IARIA will not be liable, in contract, tort (including, without limitation, negligence), pre-contract or other representations (other than fraudulent misrepresentations) or otherwise in connection with the publication of my work.

Exception to the above is made for work-for-hire performed while employed by the government. In that case, copyright to the material remains with the said government. The rightful owners (authors and government entity) grant unlimited and unrestricted permission to IARIA, IARIA's contractors, and IARIA's partners to further distribute the work.

## **Table of Contents**

| Color Invariant Study for Background Subtraction<br>Lorena Guachi, Giuseppe Cocorullo, Pasquale Corsonello, Fabio Frustaci, and Stefania Perri                                                                        | 1  |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| A Hotspot Detection Method Based on Approximate String Search<br>Shuma Tamagawa, Ryo Fujimoto, Masato Inagi, Shinobu Nagayama, and Shin'ichi Wakabayashi                                                              | 6  |

| Improving the Performance of a SOM-Based FPGA-Placement-Algorithm Using SIMD-Hardware Timm Bostelmann and Sergei Sawitzki                                                                                             | 13 |

| A Cost Model for SMARTLAM<br>Max Dobler, James Gourlay, Steffen Scholz, and Andreas Schmidt                                                                                                                           | 16 |

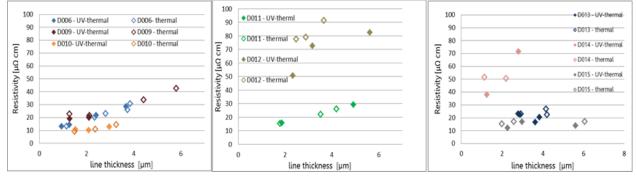

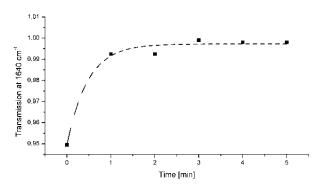

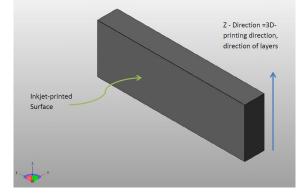

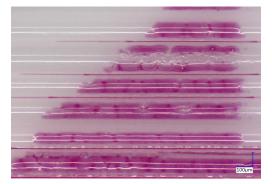

| Novel Conductive Inks for 3D Printing<br>Ayala Kabla, Leo Schranzhofer, Abd El Razek, and Fernando de la Vega                                                                                                         | 22 |

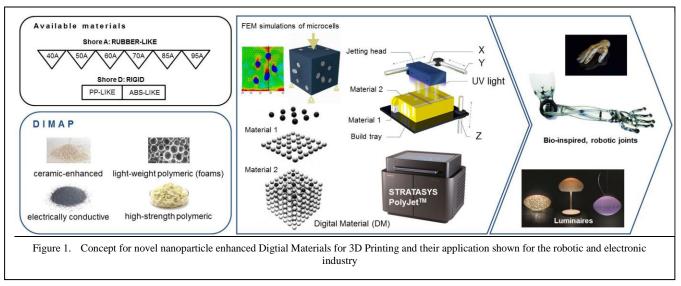

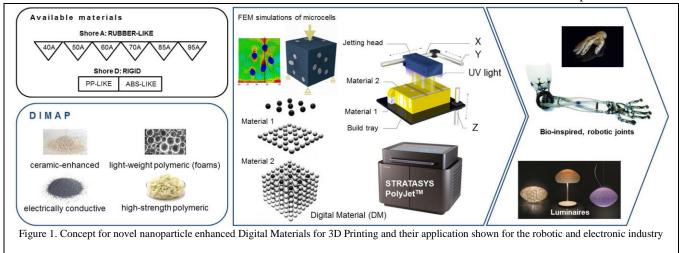

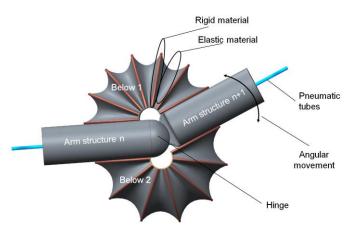

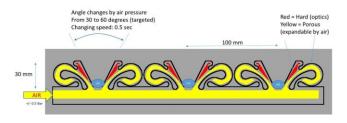

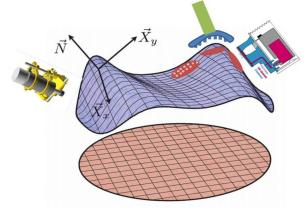

| Novel Nanoparticle Enhanced Digital Materials for 3D Printing and their Application Shown for the Robotic and Electronic Industry<br>Steffen Scholz, Adrien Brunet, Tobias Muller, and Anita Fuchsbauer               | 27 |

| Requirements for 3D Printed Applications using Novel Nanoparticle Enhanced Digital Materials<br>Adrien Brunet, Tobias Muller, Steffen Scholz, and Anita Fuchsbauer                                                    | 31 |

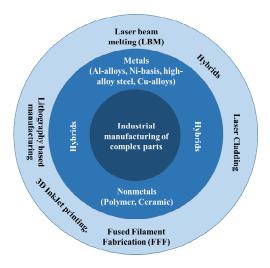

| ADDMANU – An Austrian Lighthouse Project for Additive Manfacturing<br>Christian Woegerer, Michael Muehlbereger, and Markus IKeda                                                                                      | 35 |

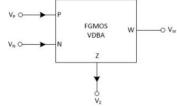

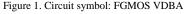

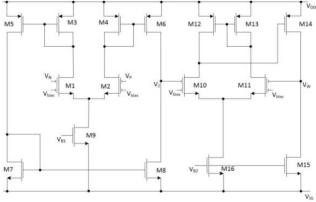

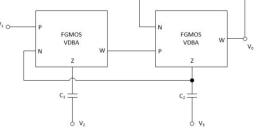

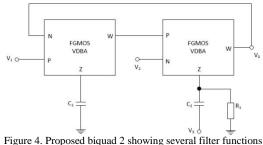

| Novel FGMOS based Voltage Differencing Buffered Amplifier and its Filter Applications<br>Akanksha Ninawe, Himani Kanwar, Richa Srivastava, and Devesh Singh                                                           | 41 |

| A High-Speed Programmable Network Intrusion Detection System Based on a Multi-Byte Transition NFA<br>Tomoaki Hashimoto, Shin'ichi Wakabayashi, Shinobu Nagayama, Masato Inagi, Ryohei Koishi, and Hiroki<br>Takaguchi | 45 |

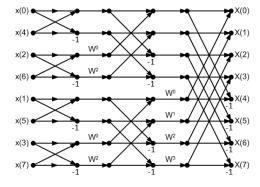

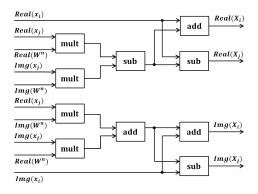

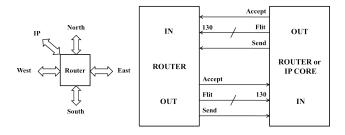

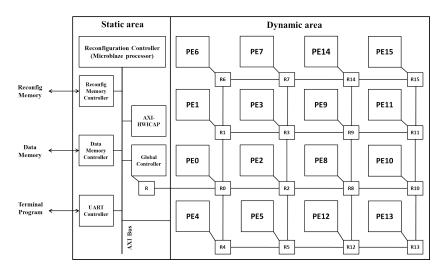

| A Dynamically Reconfigurable NoC for Double-Precision Floating-Point FFT on FPGAs Thanh Bui, Braden Phillips, and Michael Liebelt                                                                                     | 52 |

## **Color Invariant Study for Background Subtraction**

Lorena Guachi, Giuseppe Cocorullo, Pasquale Corsonello, Fabio Frustaci, Stefania Perri

Department of Electronics, Computer Sciences and Systems

DIMES - University of Calabria

Arcavacata di Rende, Italy

e-mail: loreanggeles@hotmail.com, g.cocorullo@unical.it, p.corsonello@unical.it, ffrustaci@deis.unical.it,

perri@dimes.unical.it

Abstract—Effectiveness detection to extract objects of interest is a fundamental step in many computer vision systems. In real solutions, the accurate Background Subtraction (BS) is a challenge due to diverse and complex background types. Being the color widely used as descriptor to improve accuracy in several BS algorithms, in this paper we analyze four Color Invariants (CIs) based on the Kubelka-Munk theory combined with Gray scale. The capability of several CIs combinations in segmenting foreground is evaluated referring to five video sequences. This experimental study provides a point-of-view to choose the best color combination considering accuracy and the channel numbers which can be applied for image segmentation. The results demonstrate that the combination of the color invariant H with Gray scale achieves higher performance for foreground segmentation for both indoor and outdoor video sequences. Furthermore, it uses the minimum number of color channels.

Keywords-image processing; background subtraction; color invariant.

#### I. INTRODUCTION

In the recent past, Background Subtraction (BS) has gained an extensive application as a fundamental preprocessing task of video systems especially to detect objects of interest (vehicles, people, animals and so on) for security, traffic monitoring, surveillance systems among others, which include people counting, intrusion detection and tracking [1][2].

The BS algorithms typically use five features as descriptor: color, edge, stereo, motion and texture features [2], each one having specific characteristics to handle different environments and critical situations as motion changes, viewing direction, structure background and illumination changes. In order to be more robust in presence of critical situations, some algorithms tend to combine different features. The multi-scale region BS algorithm [21] performs the Gaussian Mixture modeling in conjunction with color histograms, texture information, and consecutive division of image regions to detect efficiently edges of the moving objects. Also in [22], the use of color and edge information is applied to handle slow illumination changes and camera noise, being able to run on standard platform for real time applications.

However, the capability of segmenting moving objects from video sequences is even a challenge in vision systems, where many algorithms work for specific environments in very controlled situations. The rest of this paper is organized as follows. Section II describes most relevant related works. The color invariant descriptors are introduced in Section III. Section IV describes the algorithm used for the evaluation. The experimental results are presented in Section V. Finally, in Section VI we discuss the conclusion.

#### II. RELATED WORKS

Color features are widely used in many algorithms and the ability to be very discriminative is mainly related to the way of representing colors in the image. Different color spaces provide different accuracies [3], due to several limitations in the presence of shadows, illumination changes, and camouflage.

Several works have been proposed in order to determine which color space is best for shadow detection and BS. In [4], an experimental study is presented to show how the "RGB", "XYZ", "YCrCb", "HSV" and the normalized "rgb" formats differently affect the moving objects classification and the shadow detection. For identifying shadow edges, the color opponent space is exploited in sunlit scenes. Furthermore, it is shown that the different uniform color opponent space is the most suitable for indoor environments, and the L $\alpha$ B is an appropriate selection for both indoor and outdoor environments [5].

The influence of several color spaces on the shadow detection has been evaluated in [6]. That work demonstrated that CIE L\*u\*v color model allows moving objects to be extracted efficiently also in the presence of moving shadows. As demonstrated in [7] the color space also affects tracking methods. As an example, in tracking applications, YCbCr and HSV color models are more suitable than RGB and Grayscale color models [7].

With the main objective of improving the achieved performances and avoiding time consuming color transformation, in [9], YUV color model is exploited for shadow detection in video conference applications. On the other hand, the statistical BS algorithm proposed in [10], separates the brightness from the chromaticity component in a pixel to exploit a computational color space.

Photometric color invariants as normalized rgb, hue (H), saturation (S), 111213 and c1c2c3 are functions that describe the color configuration discounting shadows, highlight and shading. These functions are invariant to surface orientation, viewing direction and illumination conditions [8]. C1c2c3 model is adopted in [11] to exploit the spectral and geometrical characteristics for automatically shadow detection for static images and video sequences. This approach firstly hypothesizes the presence of shadows, considering some initial evidence based on the fact that shadows darken the surface which they are cast upon.

Although many works presented in the literature have demonstrated how the color features interfere in the achieved accuracy, typical descriptors are based on specifically spectral information. On the contrary, the CIs are derived from a physical model and can take into account color spectral information and color spatial structure. Therefore, focused on CIs of the Kubelka-Munk theory, in [12] the CIs H, Wx, and Wy are introduced as descriptors in a novel BS algorithm to segment several video sequences in color similar situations. A first approach to combine the CIs with different color models is introduced in [13], where particularly CI H is used in conjunction with Gray scale to build robust descriptors with the aim of reducing postprocessing task. Hence, this paper evaluates the possibility of combining the complete set of CIs (H, N, C and W) with Gray scale information. Several combinations are referenced to demonstrate that the efficiency in extraction of moving objects depends on the descriptors selected and combined through different logic operators. Overall results are presented for both indoor and outdoor experimental environments.

#### III. COLOR INVARIANT DESCRIPTOR

This section presents the fundaments of CI and Gray color space. Since the color features are often very discriminative, many BS approaches use the color as descriptor, but in certain environments it has several limitations in the presence of camouflage, shadows and illumination changes. However, the combination with other features allows achieving more robust solutions for the BS [2].

Any method for describing CI model relies on assumptions about the physical variables involved and on photometric configuration [14]. Photometric CI are characterized as a function of surface reflectance, illumination spectrum and the sensing device, which consider the spatial configuration of color, and also the color spectral energy distribution coding color information [12]. Color spaces with properties independent of illumination intensity, reflectance property, viewing direction, and object surface orientation are defined as the color invariants [8]. These properties characterize the image color configuration discounting highlights, shadows, noise and shading. As an example, the Gaussian color model with spectral and spatial parameters is exploited in [12] to define a framework for the robust measurement of colored object reflectance. The CIs are derived from a physical reflectance model based on the Kubelka-Munk theory for colorant layers [14], where, illumination and geometrical invariant properties depend of the use of reflectance model.

The invariants are useful for materials as dyed paper and textiles, paint films, opaque plastics, dental silicate cements and up to enamel. A set of CIs derived from Kubelka-Munk theory is listed in TABLE 1. The latter shows how computing the CIs named H, N, C, and W, with E,  $E\lambda$  and  $E\lambda\lambda$  being

TABLE 1.SET OF COLOR INVARIANTS

| CI | Definition                                                       |

|----|------------------------------------------------------------------|

| Н  | ελ / ελλ                                                         |

| Ν  | $(E\lambda\chi \times E - E\lambda \times E\chi) / (E \times E)$ |

| С  | Ελ / E                                                           |

| W  | Εχ / Ε                                                           |

the spectral differential quotients based on the scale-space theory [15].

The above defined CIs can be combined incrementally to achieve an alternative to invariant features extraction [14]. The Gray color space model is based on the brightness information and uses the measurement of amount of light (intensity). It is applied for object tracking often on a blob or a specific region [7]. However, taking into account that the color furnishes more information on the objects in a scene, it would be expected that this model can be used in conjunction with other models to achieve more robust solutions and higher accuracy than the basic separated models. For this reason, the Gray color space is included in the study here presented with the additional advantage of using a color space that does not require complex color transformations.

#### IV. BACKGROUND SUBTRACTION ALGORITHM

The main computational steps required to classify the foreground pixels by using CIs can be summarized as follows: 1) RGB input frames are processed to obtain the CIs; 2) the background model is initialized by collecting, as the historical frames, the CIs obtained for the first *Nf* frames and the current background is computed; 3) as soon as the (Nf+1)-th frame is acquired, the foreground detection initiates and it is executed pixel-by-pixel by comparing the CIs of the current pixel the CIs of historical frames; 4) the current background model is updated taking into account the obtained classification.

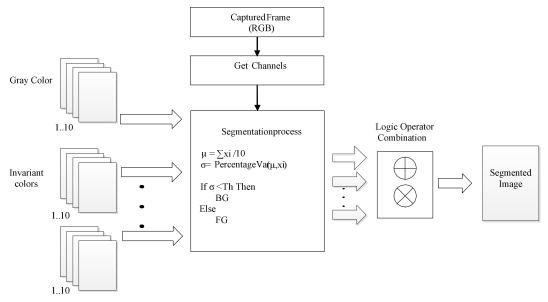

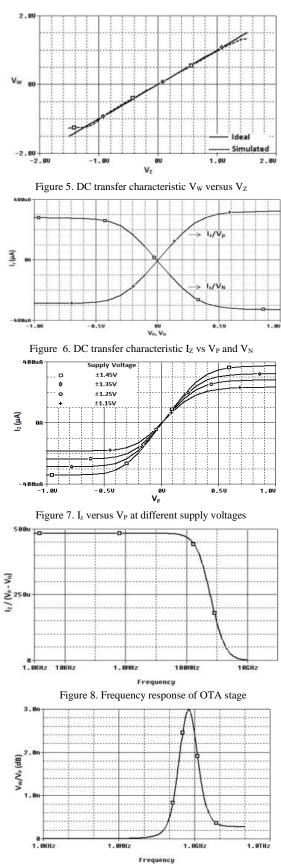

To study the performance of CIs defined in Section III, we reference the algorithm schematized in Figure 1, which uses only ten historical frames. Some evaluated combinations of the features selected include a channel with Gray scale information whereas others are compounded only by CIs. Each channel is analyzed separately computing the percentage variation between the current frame and the historical mean. To classify the pixels within the generic frame of a video sequence into the background and the foreground sets, a thresholding is performed for each adopted descriptor. In our study, we refer to H, W, N, C and Gray scale components with the threshold values Th=55, Tw=90, Tn=90, Tc=90, Tg=60 that have been set experimentally to the values for which the number of wrong classified pixels is minimized for typical benchmark video sequences [17-20]. Several tests have demonstrated that higher threshold values reduce the accuracy in detecting foreground pixels, whereas smaller values increase the noise

Figure 1. Background Subtraction diagram overview.

sensitivity. As suggested in [3], Nf=10 is initially used to model the background with a single Gaussian distribution. Several experiments demonstrated that increasing Nf does not significantly improve the accuracy but increases the memory requirement. Each component of the generic pixel of the current frame is compared to the mean value computed for the correspondent channel of historical frames. When the difference between the current examined channel and the historical mean overcomes the relative threshold, the current component is classified as belonging to a foreground pixel. Otherwise it is recognized as the component of a background pixel. Partial results obtained separately from the examined channels are then combined through appropriate logic operators to obtain the final segmented images. Background model is updated introducing a new frame at position zero, and discarding the oldest frame of position nine, all frames are sorted after each analysis.

#### V. EXPERIMENTAL RESULTS

C++ software routines have been on purpose implemented to evaluate twenty three color combinations. Experimental tests have been done on different video sequences, related to both indoor and outdoor environments and the achieved performances are measured in terms of recall (Rec), specificity (Sp), precision (Pr), and percentage of correctly classified pixels (PCC). Rec measures the accuracy of the approach at the pixel level with a low False Negative Rate;

TABLE 2. COMPARISON RESULTS

| Combination | Rec   | Sp    | Pr    | PCC   |

|-------------|-------|-------|-------|-------|

| H AND GRAY  | 11.13 | 99.77 | 81.82 | 93.88 |

| H OR GRAY   | 52.65 | 89.87 | 27.61 | 87.50 |

| Combination                    | Rec   | Sp    | Pr    | PCC   |

|--------------------------------|-------|-------|-------|-------|

| H AND N                        | 13.58 | 98.31 | 33.87 | 92.68 |

| H OR N                         | 54.60 | 82.18 | 18.08 | 81.74 |

| (H OR N) AND GRAY              | 13.19 | 99.72 | 81.13 | 93.98 |

| (H OR N) OR GRAY               | 59.34 | 82.10 | 19.27 | 80.68 |

| H AND C                        | 19.95 | 96.17 | 29.22 | 91.07 |

| H OR C                         | 50.09 | 85.77 | 26.24 | 83.40 |

| (H OR C) AND GRAY              | 15.08 | 99.07 | 79.21 | 93.44 |

| (H OR C) OR GRAY               | 56.93 | 89.11 | 27.61 | 87.13 |

| H AND W                        | 9.27  | 98.67 | 31.63 | 92.79 |

| H OR W                         | 59.79 | 76.14 | 15.44 | 76.41 |

| (H OR W) AND GRAY              | 13.70 | 99.72 | 81.33 | 94.03 |

| (H OR W) OR GRAY               | 64.02 | 76.06 | 16.26 | 75.30 |

| H OR N OR C                    | 64.08 | 75.50 | 15.97 | 74.77 |

| (H OR N OR C )<br>OR GRAY      | 68.49 | 70.14 | 14.34 | 70.05 |

| (H OR N OR C)<br>AND GRAY      | 15.09 | 99.70 | 81.60 | 94.13 |

| H OR N OR W                    | 65.31 | 70.20 | 13.78 | 69.84 |

| (H OR N OR W)<br>AND GRAY      | 14.76 | 99.70 | 81.15 | 94.09 |

| (H OR N OR W) OR<br>GRAY       | 66.92 | 75.44 | 16.47 | 74.93 |

| H OR N OR C OR W               | 68.76 | 69.63 | 14.19 | 69.59 |

| (H OR N OR C OR W)<br>AND GRAY | 15.74 | 99.68 | 81.33 | 94.16 |

| (H OR N OR C OR W)<br>OR GRAY  | 70.95 | 69.59 | 14.54 | 69.72 |

Sp stimulates combinations with a low False Positive Rate; Pr favors combinations with a low False Positive Rate, and PCC measures the percentage of correct classifications [17]. The overall results are summarized in Table 2. The first column shows the logic operation applied to classify foreground pixels. As an example, the combination (H OR W) AND GRAY detects the generic pixel as foreground only if either its component H or its component W belongs to a foreground pixel, and also its Gray scale data is associated to a foreground pixel.

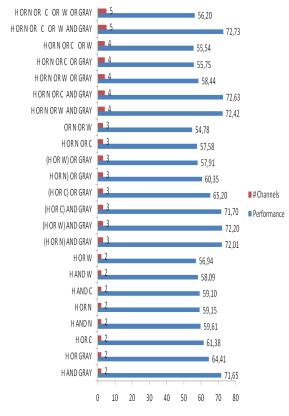

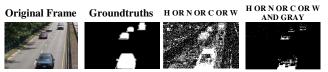

The results presented in Table 2 show that, as expected, differently combining CIs with Gray scale data very different accuracy can be achieved in detecting foreground objects. It is worth pointing out that the number of channels used to achieve a given accuracy significantly affects the computational complexity. In Figure 2. , the average accuracy obtained with each combination is directly related to the number of channels involved. Based on numeric analysis we can see that the combination (*H* OR *N* OR *C* OR *W*) AND *GRAY* achieves the best accuracy for indoor and outdoor experimental environments, and focused on the number of channels, the set of *H* AND *GRAY* reaches good performance on average with the minimum number of color channels. Figure 3. shows some of the segmented images obtained with these two combinations.

The results depicted in Figure 4 show the benefits achieved by introducing Gray scale in the set of CI combination to reduce the noise and improve the accuracy.

Figure 2. Analysis of the adopted combinations.

Figure 3. Results related to: a) Highway; b) Fountain; c) Pets2006; d)Bootstrap; e)Office.

Figure 4. Results obtained introducing Gray scale information

All the above results have been obtained through the hardware system illustrated in Figure 5. The latter is based on the Raspberry Pi equipped with a camera module, able to capture RGB and grayscale images, and a Broadcom BCM2835 system on chip, consisting of an ARM1176JZF-S 700 MHz processor, a VideoCore IV GPU, 512 MB of RAM, and an SD card for long term storage and booting.

Figure 5. The hardware system used for tests

#### VI. CONCLUSION

This paper has empirically compared the suitability of sets of CI combinations. Some of them include Gray scale. The tests measured the performance of the combinations referring to indoor and outdoor experimental environments, demonstrating that the Gray scale insertion mitigates the problem of misclassified pixel. H and Gray scale combination provides the highest performance with respect to other combinations with the benefit of include particularly only two channels. Gray color model leads to background with less noise. On the contrary, CIs increase the noise due to the transformation operations, but, the combination with Gray color space allows achieving high effectiveness in the BS. These characteristics can be efficiently introduced in the algorithms for the image segmentation.

#### REFERENCES

- A. Sobral and A. Vacavant, "A comprehensive review of background subtraction algorithms evaluated with synthetic and real videos," Computer Vision and Image Understanding, vol. 122, pp. 4-21., 2014.

- [2] T. Bouwmans, "Traditional and recent approaches in background modeling for foreground detection: An overview," Computer Science Review, vol. 11, pp. 31 – 66, 2014.

- [3] H. Zhou, Y. Chen, and R. Feng, "A novel background subtraction method based on color invariants," Computer Vision and Image Understanding, vol. 117, no 11, pp. 1589– 1597, 2013.

- [4] P. Kumar, K. Sengupta, and A. Lee, "A comparative study of different color spaces for foreground and detection for traffic monitoring system," In Intelligent Transportation Systems, 2002. Proceedings. The IEEE 5th International Conference on. IEEE, pp. 100-105, 2002.

- [5] E. Khan and E. Reinhard, "Evaluation of color spaces for edge classification in outdoor scenes," In Image Processing, 2005. ICIP 2005. IEEE International Conference on. IEEE,, pp. III-952-5, 2005.

- [6] C. Benedek and T. Szirányi, "Study on color space selection for detecting cast shadows in video surveillance," International Journal of Imaging Systems and Technology, vol. 17, no 3, pp. 190-201, 2007.

- [7] P. Sebastian, Y. Vooi, and R. Comley, "Colour space effect on tracking in video surveillance," International Journal on Electrical Engineering and Informatics, vol. 2, no 4, pp. 298-312, 2010.

- [8] T. Gevers and A. W. M. Smeulders, "Color-based object recognition," Pattern Recognition, vol. 32, no 3, pp. 453– 464, 1999.

- [9] O. Schreer, I. Feldmann, U. Goelz, and P. Kauff, "Fast and robust shadow detection in videoconference applications," in Video/Image Processing and Multimedia Comuunications 4th

EURASIP-IEEE Region 8 International Symposium on VIPromCom. IEEE, , pp. 371–375, 2002.

- [10] T. Horprasert, D. Harwood, and L.S. Davis, "Statistical approach for real-time robust background subtraction and shadow detection," In Proceedings IEEE International Conference on Computer Vision, pp. 1-19, 1999.

- [11] E. Salvador, A. Cavallaro, and T. Ebrahimi, "Cast shadow segmentation using invariant color features," Computer vision and image understanding, vol. 95, no 2, pp. 238-259, 2004.

- [12] H. Zhou, Y. Chen, and R. Feng, "A novel background subtraction method based on color invariants," Computer Vision and Image Understanding, vol. 117, no 11, pp. 1589– 1597, 2013.

- [13] L. Guachi, G. Cocorullo, P. Corsonello, F. Frustaci, and S. Perri, "A novel background subtraction method based on color invariants and grayscale levels," In Security Technology (ICCST), 2014 International Carnahan Conference on. IEEE, pp. 1-5, 2014.

- [14] J. M. Geusebroek, R. van den Boomgaard, A. W. M. Smeulders, and H. Geerts, "Color invariance," Pattern Analysis and Machine Intelligence, IEEE Transactions On, vol. 23, no 12, pp.1338-1350,2001.

- [15] L. M. J. Florack, B.M. ter Haar Romeny, J.J. Koenderink, and M.A. Viergever, "Scale and the Differential Structure of Images," Image and Vision Computing, vol. 10, no. 6, pp. 376-388, 1992.

- [16] R. Gonzalez and R. E. Woods, "Digital Image Processing using Matlab," 2004: Pearson Prentice Hall.

- [17] N. Goyette, P. M. Jodoin, F. Porikli, J. Konrad, and P. Ishwar, "Changedetection. net: A new change detection benchmark dataset," In Computer Vision and Pattern Recognition Workshops (CVPRW), 2012 IEEE Computer Society Conference on. IEEE, pp. 1-8, 2012.

- [18] Statistical Modeling of Complex Background for Foreground Object Detection. [Online]. Available from: http://perception.i2r.a-star.edu.sg/bk\_model/bk\_index.html. [accessed July 2016]

- [19] Test Images for Wallflower Paper. [Online]. Available from: http://research.microsoft.com/enus/um/people/jckrumm/wallflower/testimages.htm. [accessed July 2016]

- [20] ChangeDetection.NET (CDNET). [Online]. Available from: http://www.changedetection.net. [accessed July 2016]

- [21] P. D. Z. Varcheie, M. Sills-Lavoie, and A. Bilodeau, "A multiscale region-based motion detection and background subtraction algorithm," Sensors, vol. 10, no 2, pp. 1041-1061, 2010.

- [22] S. Jabri, Z. Duric, H. Wechsler, and A. Rosenfeld, "Detection and location of people in video images using adaptive fusion of color and edge information," In Pattern Recognition, 2000. Proceedings. 15th International Conference on. IEEE, pp. 627-630, 2000.

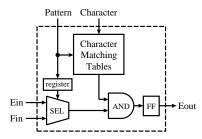

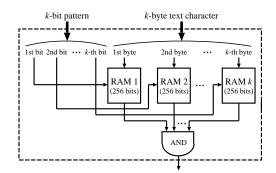

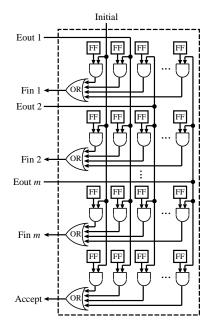

## A Hotspot Detection Method Based on Approximate String Search

Shuma Tamagawa\*, Ryo Fujimoto<sup>†</sup>, Masato Inagi<sup>‡</sup>, Shinobu Nagayama\*, Shin'ichi Wakabayashi\*

\*<sup>‡</sup>Graduate School of Information Sciences, Hiroshima City University

<sup>†</sup>Faculty of Information Sciences, Hiroshima City University

3-4-1 Ozuka-higashi, Asaminami-ku, Hiroshima, 731-3194 Japan

Email: <sup>‡</sup>inagi@hiroshima-cu.ac.jp

Abstract—In this paper, we propose an approximate string searchbased method for detecting hotspots on mask patterns used in very-large-scale integration (VLSI). In mask patterns for manufacturing VLSI chips, there are some local patterns which induce open/short circuits and thus failures. Such patterns are called hotspots. They are detected by optical simulation before manufacturing. Since it, however, requires very long time, it is desirable to detect hotspot candidates in order to limit the target regions of optical simulation. For the detection, methods which check matching between each pattern from a pre-defined hotspot library and the mask pattern are attracting attention. At first, our proposed method transforms the mask pattern and the predefined hotspot patterns, which are two-dimensional, into onedimensional strings. Then, it finds hotspot candidates by using approximate string search to detect patterns similar to hotspot patterns. The transformation is performed in a particular way to efficiently realize quasi-two-dimensional search by using string search. In addition, we focus on the distance between wires as a metric to find hotspot candidates, and give a priority to patterns which have wires with a shorter distance. To evaluate the effectiveness of our method, we conducted some experiments.

# Keywords–lithography; hotspot; optical simulation; approximate string matching.

#### I. INTRODUCTION

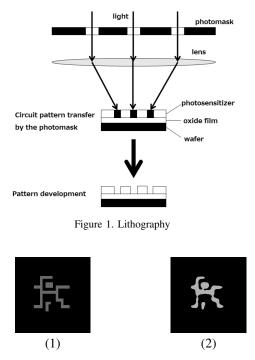

In recent decades, the density of semiconductor chips has greatly been increased with advances in very-large-scale integration (VLSI) technology. In lithography process for manufacturing VLSI chips [1], the circuit pattern (mask pattern) drawn on a photomask is transferred to a silicon wafer using photolithography machine. While 193nm wave length laser is currently used for the lithography process, the minimum pitch between wires is becoming smaller and has reached 14nm. Thus, because of diffraction during exposure, transfer of the mask pattern drawn on the photomask to the wafer sometimes fails. Hotspot is a place on the mask pattern where such a failure of transfer is likely to occur.

For manufacturing VLSI chips, a photomask is necessary. However, the manufacturing cost of the photomask is very high. To avoid remanufacturing photomasks, it is desirable to remove hotspots before manufacturing the photomask. Thus, optical simulation is conducted to detect hotspots. However, it takes very long time to conduct the optical simulation to the entire mask pattern. It is possible to shorten the simulation time by applying the optical simulation only to the hotspot candidates on the mask pattern. Thus, some methods for detecting hotspot candidates have been studied [2]-[6].

The method proposed in [2] is based on pattern matching [7]. The others [3]-[6] build a decision model, such as artificial

neuron network, by learning hotspot/non-hotspot patterns, and detect hotspot candidates based on the model. [8] summarized related work including most of the methods.

In this study, we consider a method which conducts twodimensional pattern matching by using string matching. In string matching, there are a lot of variation problems. String search problems are its variations to find the substrings same to a given pattern in a given string. An algorithm proposed by Knuth et al. [7] is well-known as an algorithm for the basic problem of string search. Hardware algorithms for the problems also have been proposed [9]-[11]. Our proposed method is based on approximate string search [12][13], which is a variation of string search and in which substrings similar to a given pattern are searched in a given string. Our method conducts approximate string search by transforming the twodimensional mask pattern and the two-dimensional hotspot patterns into one-dimensional strings. When transforming these patterns, it is necessary to pad a lot of don't care characters to the hotspot patterns in order to match the widths of the mask and hotspot patterns. For efficient string search, we introduce a quantitative don't care character which represents a number of consecutive don't care characters. In addition, we confirmed that a pattern (in the mask pattern) similar to a hotspot pattern is more likely to be a hotspot if there are two wires in the pattern whose distance is smaller than that between the corresponding wires in the hotspot pattern. Thus, we propose a hotspot detection considering the distance between wires. Finally, we confirm the effectiveness of our proposed method comparing with a method based on two-dimensional simple matching.

The rest of this paper is organized as follows. First, in Section II, lithography, hotspot detection problem and related work, approximate string search problem, and an algorithm for the string matching problem are explained. Section III presents our hotspot detection method based on approximate string search. In Section VI, experimental results are shown. Finally, conclusions are described in Section V.

#### II. PRELIMINARIES

#### A. Lithography

Lithography (photolithography) is one of the processes for VLSI manufacturing, and a technology to transfer a circuit pattern drawn on a photomask, which is the master to replicate the circuit pattern, to a silicon wafer using a photolithography machine (exposure device).

The basis of lithography is shown in Figure 1. In lithography process, light is shed on the photomask and the mask

Figure 2. Hotspot: (1) a hotspot pattern, (2) transferred image

pattern drawn on the photomask is transferred to the wafer via lenses. While 193nm wave length laser is currently used for the lithography process, the minimum pitch between wires is becoming smaller and has reached 14nm. Thus, diffraction occurs during exposure. For this reason, there are cases in which the mask pattern drawn on the photomask cannot be correctly transferred to the wafer. Hotspot is a place on the mask pattern where such a failure of transfer is likely to occur. Let us consider a pattern (1) in Figure 2 as an example. Figure 2 (2) is a transferred image of the pattern (1). In the image (2), wires are fused at an unintended position. Thus, the pattern (1) is a pattern which induces a failure and considered as a hotspot.

#### B. Hotspot Detection Problem

There exist two problems relating to hotspots: hotspot decision and hotspot detection (hotspot search). Hotspot decision problem is to determine whether a given small pattern is a hotspot (candidate) or not, while hotspot detection problem is to detect hotspots (hotspot candidates) from a given large mask pattern. In hotspot detection problems, a mask pattern and a known hotspot pattern (or a set of known hotspot patterns) are given, and patterns similar to the known hotspot pattern (or one of the known hotspot patterns) are searched in the mask pattern.

#### C. Related Work

Most existing methods [2]-[6] solve a hotspot detection problem by scanning the mask pattern and solving hotspot decision problems.

The existing methods can be classified into [2], [3][4], and [5][6]. The main difference among the three groups is the information used for detection. In [2], a binary image of

a pattern is encoded to a vector and used for detection. In [3][4], information such as the length and width of each wire is extracted from the pattern, and encoded to a vector. In [5][6], a pattern is encoded as a density-based data, and used for detection.

From another viewpoint, the existing methods can briefly be explained by their base algorithms: [2] is based on pattern matching, [3] is based on machine learning, [4] is a hybrid method combining machine learning and pattern matching, and [5][6] are based on fuzzy matching.

Here, we explain the overview of each group of the existing methods. In this paragraph, we describe the flow of a pattern matching-based method [2]. First, overlay a coarse grid on the mask pattern. Then, grid points on wire segments are colored. The coloring of the grid is transformed into a matrix, and then it is again transformed into a vector. Each hotspot pattern is transformed into vector in the same way. Then, the mask pattern vector and a hotspot pattern vector are matched by using the Knuth-Morris-Pratt (KMP) string matching algorithm [2][7]. If a hotspot pattern vector matches a part of the mask pattern vector, range pattern matching (RPM) is performed to them using a finer grid. In RPM, users can specify the ranges of the length and width of a segment of a wire in the hotspot pattern, etc., and thus flexible matching can be realized. This method realizes high accuracy by the hierarchical matching, in addition to low memory usage by the coarse global grid.

Second, we describe the flow of a machine learning-based method [3]. First, extract feature quantities for each known hotspot pattern considering the length, width, etc. of wire segments in the pattern, and construct a compact vector from the feature quantities of each pattern. Then, hierarchically build both artificial neural network (ANN) models and a support vector machine (SVM) models training by the vectors for accurate and robust decision-making. Then, a target pattern is applied hierarchical machine learning-based matching using the hierarchical model. This method realizes high accuracy, high robustness and low false-alarm ratio by the hierarchical model, in addition to short runtime by their compact feature vectors.

Next, we describe the flow of a hybrid method [4]. First, perform pattern matching for a target pattern and the hotspot patterns. If it matches one of the hotspot patterns, they conclude that it is a hotspot. Otherwise, matching based on machine learning is performed to the pattern. A pattern which is determined as a non-hotspot pattern which is determined as a hotspot. A pattern which is determined as a hotspot pattern is applied machine learning-based matching again, using a different machine learning model to accurately examine if it is likely to be a hotspot or not. Only if it is determined as a hotspot by the second machine learning-based matching, they conclude that it is a hotspot. This method realizes high accuracy and short runtime by its hybrid strategy.

Then, we explain the common flow of fuzzy matchingbased methods [5][6]. First, divide the mask and pre-defined hotspot patterns into tiles and calculate the density of wires in each tile as a feature quantity of the tile. Next, build a fuzzy matching model from the vectors of the feature quantities of the hotspot patterns. To build the model, calculate a distance, called city block distance (CBD), between every two hotspot patterns. If the CBD between two hotspot patterns is smaller than a threshold, they are placed in the same hotspot group. Next, a fuzzy region is extracted from each hotspot group in the fuzzy space. Then, fuzzy regions are expanded as far as they are legal as fuzzy regions. This is necessary to divide the fuzzy space into hotspot regions and non-hotspot regions in a fuzzy manner. Finally, determine if a given pattern is a hotspot or not, using the fuzzy matching model. If an inequality is satisfied on the model with a given pattern, it is determined as a hotspot. When building and using the model, a heavy weight is imposed to the center area of each pattern, because failures occur in the center area of hotspot patterns with a higher possibility than outside the center area. For hotspot detection in [5][6], candidate patterns, which include suspicious polygons (wires), are extracted and applied fuzzy matching. This method realizes high accuracy and low false-alarm ratio when using fine tiles.

Our proposed method is based on string matching. In the method, every pixel image of the mask and known hotspot patterns is sliced and converted into a string, and then approximate string search is performed. We expect that approximate string search realizes more flexible hotspot search since it can find not only the substrings exactly same as the given pattern but also similar substrings. Before approximate string search, each known hotspot pattern is analyzed, and congested areas, where wires are close to each other, are given heavy weights to find severe patterns in priority. We consider a hierarchical approach, which most existing methods employ, is promising. Therefore, this study is the first step of an attempt to develop a better method to replace a stage of hierarchical methods.

#### D. Approximate String Matching Problem

Approximate string matching problem [12][13] is one of the string matching problems, and is a problem to determine if two given strings are similar or not. In this study, the similarity between strings is measured by the edit distance explained in the next subsection. If the edit distance is less than or equal to a given threshold, we consider they are similar each other.

#### E. Edit Distance

Let us consider a pair of characters  $(a, b) \neq (\epsilon, \epsilon)$ , where  $\epsilon$  is an *empty character*, which represents nonexistence of any character. The operation transforming character a in a string into b is called an *edit operation*, and is denoted by  $a \rightarrow b$ . For example, let us consider a string A = qzh. If an edit operation  $g \to f$  is applied to the first character of A, we get A' = fzh as the resultant string of the operation. If an edit operation  $z \to \epsilon$  is applied to the second character of A, we get A' = gh. If an edit operation  $\epsilon \to j$  is applied to the empty character between the second and third characters of A, we get A' = qzjh. Hereinafter, we call an operation  $a \rightarrow b$  a substitution if  $a \neq \epsilon$  and  $b \neq \epsilon$ . Likewise, we call an operation  $a \to \epsilon$  a *deletion*, and call an operation  $\epsilon \to b$ an insertion. Any string can be transformed into an arbitrary string by applying the edit operations. An edit operation has its cost denoted by  $\gamma(a \rightarrow b)$ . We assume the costs of edit operations satisfy the equation below.

$$\begin{split} \gamma(a \to a) &= 0 \\ \gamma(a \to b) + \gamma(b \to c) \geq \gamma(a \to c) \end{split}$$

Suppose strings A and B on alphabets  $\Sigma$  are given. A sequence of edit operations to transform A into B is denoted as S =

$s_1, s_2, \ldots, s_m$ . The cost of S is defined as

$$\gamma(S) = \sum_{i=1}^{m} \gamma(s_i).$$

The minimum value among the costs of all the sequences each of which transforms A into B is defined as *the edit distance between* A and B [12].

#### F. Approximate String Search Problem

Approximate string search is to find substrings similar to a given pattern in a long input sequence. More precisely, approximate string search is to find all the substrings whose edit distance to the pattern P are the minimum among all the substrings (or less then the given threshold k), in the input sequence S.

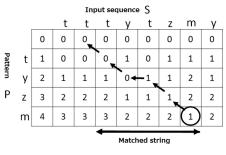

We here explain a dynamic programming-based algorithm for approximate string search [12][13]. Prepare an  $(n + 1) \times$ (m + 1) two-dimensional array D, where n is the length of the pattern  $P = a_1a_2 \cdots a_n$ , and m is the length of the input sequence  $S = b_1b_2 \cdots b_m$ . The element D(i, j) of D is defined by the equation below. Then,  $D(n, j)(1 \le j \le m)$  give the edit distances of substrings from the pattern. If the value is the minimum among all the  $D(n, j)(1 \le j \le m)$  (or less than the user-defined threshold k), substrings whose terminal is  $b_j$  are considered as those similar to the pattern. The initials of the substrings can be found by backtracing on D. The details of the identification of similar substrings of our proposed method are explained later.

$$D(0,0) = 0, D(0,j) = 0,$$

$$D(i,0) = D(i-1,0) + del(a_i),$$

$$D(i,j) = \min\{D(i-1,j) + del(a_i),$$

$$D(i,j-1) + ins(b_j),$$

$$D(i-1,j-1) + sub(a_i,b_j)\}$$

$$sub(a_i,b_j) = \gamma(a_i \to b_j),$$

where the function *ins*, *del*, and *sub* denote the insertion, deletion, and substitution costs.

Let us consider an example of searching substrings of S = tttytzmy similar to P = tyzm. Here, we set the every cost of the insertion, deletion and substitution operations to 1. Then, we obtain an array D shown in Figure 3 from the recursive definition of D(i, j). Next, we search the minimum element of the bottom row of D. In this example, D(4,7) = 1has the minimum value. Next, we trace the edit operations back from the element. If a deletion operation was applied there, *i.e.*, the minimum function in the recursive definition chose a deletion operation, we move to the upper element. Likewise, if an insertion (substitution) operation was applied there, we move to the left (upper-left) element. Finally, we obtain S < 3, 7 >= tytzm as a substring similar to the pattern P, where  $S < i, k >= b_i b_2 \cdots b_k$ . As shown in the example, in approximate string search, substrings similar to the pattern are found by calculating the edit distances from the middle of the input sequence. The time-complexity of this algorithm is O(nm).

Figure 3. Edit distance array D

Figure 4. Image data and its corresponding array

#### III. HOTSPOT DETECTION BASED ON APPROXIMATE String Search

In this section, we present our hotspot detection method based on approximate string search. In this method, the mask pattern and a hotspot pattern, which are both two-dimensional data, are transformed into one-dimensional strings to apply approximate string search calculating array D by dynamic programming. In addition, we propose an extension of the method to give priority to be picked up to patterns more likely to be hotspots.

#### A. Transformation into One-dimensional Data

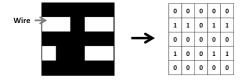

Mask patterns and hotspot patterns are image data. We transform them into two-dimensional array of characters, in which wire area is represented by 1 and empty area is represented by 0.

An example is shown in Figure 4. In the left image in it, white areas show wires, and black areas show empty areas.

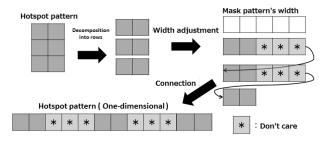

We transforms the two-dimensional arrays into onedimensional data. In the transformation of the mask pattern, the two-dimensional array of the mask pattern is divided into rows. Then, the tail of the first row and the head of the second row is connected. And, the tail of the second row is connected to the head of the third row. Connecting all the rows according to the procedure, the two-dimensional mask pattern data is transformed into one-dimensional data. Next, we explain how to transform the two-dimensional hotspot pattern into one-dimensional data. The procedure of the transformation is shown in Figure 5. First, the array of the hotspot pattern is divided into rows, like the transformation of the mask pattern. Next, don't care characters are inserted to each row to fit the width of the hotspot pattern to that of the mask pattern. Then, the rows are connected into one-dimensional data, like the procedure of the mask pattern.

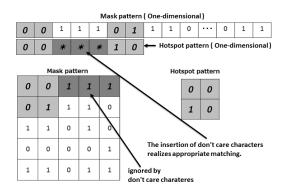

The insertion of don't care characters virtually realizes twodimensional matching by one-dimensional matching. Figure 6 illustrates hotspot search with don't care characters. A don't care character can be represented by setting its substitution

Figure 5. Transformation of hotspot data

Figure 6. Matching after inserting don't care characters

cost to 0. To make the explanation simple, let us consider the case of matching the two-dimensional data (i.e., not searching but matching). By padding don't care characters to the onedimensional data of the hotspot pattern in order to fit the width of the hotspot pattern to that of the mask pattern, the values of the elements of the hotspot pattern and the values of the elements in the corresponding area of the two-dimensional mask pattern are matched (i.e., compared). In the figure, the values from the third element to the fifth element in the first row of the mask pattern are matched with the inserted don't care characters in the hotspot pattern. (That is, the values from the third element to the fifth element of the mask pattern are ignored.) Therefore, the values from the first element to the second element in the second row of the two-dimensional mask pattern are appropriately matched with the values from the first element to the second element in the second row of the two-dimensional hotspot pattern by one-dimensional matching. This way, the hotspot pattern is matched with the corresponding area of the two-dimensional mask pattern.

#### B. Dynamic Programming

In our method, since hotspot candidates are searched by using approximate string search, array D is calculated by using the dynamic programming shown in the previous section. Except the first row and column, the value of each element of the array D is calculated by using the value of its upper, left and upper-left elements. These calculations are done line by line from the top to the bottom.

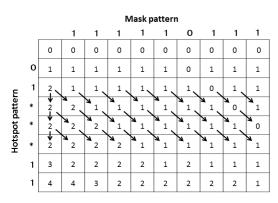

Let us focus on the calculation of the element where the character of the hotspot pattern is don't care. In the case, consecutive x don't care characters require x rows of the calculations. Figure 7 illustrates the calculation of array

Figure 7. Calculation of array D with consecutive don't care characters

|                 | Mask pattern |               |                 |    |                   |               |                    |               |             |             |              |

|-----------------|--------------|---------------|-----------------|----|-------------------|---------------|--------------------|---------------|-------------|-------------|--------------|

|                 |              |               | 1               | 1  | 1                 | 1             | 1                  | 0             | 1           | 1           | 1            |

|                 |              | 0             | 0               | 0  | 0                 | 0             | 0                  | 0             | 0           | 0           | 0            |

| _               | 0            | 1             | 1               | 1  | 1                 | 1             | 1                  | 0             | 1           | 1           | 1            |

| ttern           | 1            | 2             | 1               | 1  | 1                 | 1             | 1                  | 1             | 0           | 1           | 1            |

|                 |              |               |                 | _  |                   |               |                    |               |             |             |              |

| oot pai         | *3           | 2 -           | → 2 -           | →2 | <b>→</b> 2        | 7             | <b>11</b>          | 71            | <b>*</b> 1  | <b>→</b> 1  | →1           |

| Hotspot pattern | *3<br>1      | 2 -<br>3      | 2 −             | →2 | 2 2               | <b>1</b><br>2 | <b>7</b> 1<br>1    | <b>1</b><br>2 | <b>1</b>    | <b>1</b>    | → <u>1</u>   |

| Hotspot pa      |              | 2 -<br>3<br>4 | → 2 - 2 - 2 - 4 |    | *2<br>2<br>2<br>2 | 2<br>2<br>2   | <b>1</b><br>1<br>2 | 1<br>2<br>2   | 1<br>1<br>2 | 1<br>1<br>2 | *1<br>1<br>1 |

Figure 8. Calculation of array D with a large don't care character

D with consecutive don't care characters. In our method, such consecutive x don't care characters are merged to one character, called a *large don't care*. If the character of the hotspot pattern is a don't care character, each element of the corresponding row is equal to its upper-left element. (Each element of the leftmost column is equal to its upper element.) On the other hand, if the character of the hotspot pattern is with a large don't care character, each element of the corresponding row is equal to the element at the x-th left column at the upper row. In this way, x lines of calculations of a large don't care character. Figure 8 illustrates the calculation of array D with a large don't care character.

#### C. Detection of Hotspot Candidates

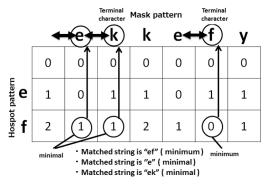

After calculating array D, substrings similar to the hotspot pattern are detected as hotspot candidates. To detect hotspot candidates, first, we focus on the elements with the minimum value in the bottom row of D. Each of these elements is considered as the terminal character of a hotspot candidate. Since we assume the hotspot candidate has the length same as the hotspot pattern, the initial character can be identified from the terminal character. The assumption is based on the fact that a hotspot pattern and candidates similar to the pattern are originally two-dimensional images, and have the same size or almost same sizes. Next, we focus on the elements with the minimal values in the bottom row of D. The elements whose values are less than or equal to a use-defined value (threshold) k are chosen from the elements with the minimal values, and processed in the same way.

Figure 9. Detection of hotspot candidate

Figure 9 illustrates an example of hotspot candidate detection. First, the minimum values in the bottom row of array D are found. In Figure 9, the value 0 of the 6th column is the minimum. The column with the minimum value corresponds to the character f of the mask pattern. Thus, the substring ef which has the terminal character f and the length same as the pattern ef is detected as a hotspot candidate. Next, the minimal values no more than the threshold k in the bottom row of array D are found. In this example, we set k = 1. The second and third columns in the bottom row satisfy the condition. Thus, the substring  $e(= \epsilon e)$  whose terminal is in the second column is found as a hotspot candidate. Likewise, the substring ek whose terminal is in the 3rd column is found as a hotspot candidate.

It seems that array D requires a large amount of memory area. However, since we need only the bottom raw of D to detect the hotspot candidates, the memory area for each raw (except the bottom raw) can be released after the calculation of the next raw. That is, we need to memorize only the current and previous rows at a time.

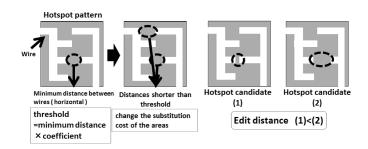

#### D. Detection of Severe Patterns Considering Distance between Wires

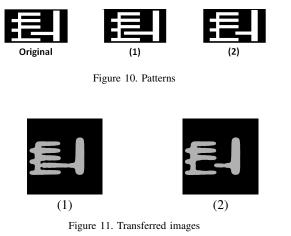

Hotspot patterns are those which induce short or open circuits. If there exist patterns in the mask pattern similar to a hotspot pattern, they are likely to be hotspots. We focus on the distance between wires as a measure to determine the criticality of hotspot candidates. We performed simulations for two patterns by using an optical simulator [14]. The results of the simulations for the patterns (1) and (2) in Figure 10 are shown in Figure 11 (1) and (2), respectively. In Figure 10, pattern (1) and (2) are variations of the original hotspot pattern. In pattern (1) ((2)), the horizontal distance between the left and right wires is shorter (longer) than the original one (the horizontal segment of the right wire is longer (shorter) then that of the original one). As shown in Figure 11, pattern (1) clearly caused a short circuit, and thus it is a hotspot. Although pattern (2) might be a hotspot, too, it is not clear from the simulation. These results indicate that among patterns which have the same similarity to the original hotspot pattern, patterns with shorter distances between wires are more critical. Therefore, we propose an extension of our hotspot detection method to detect more critical patterns in priority among patterns with the same similarity, considering the distances between wires.

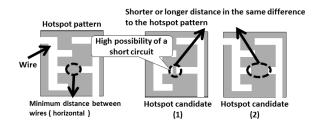

Let us consider two hotspot candidates similar to a hotspot

pattern. There exists the (horizontally) shortest distance between wires in the hotspot pattern. One of the hotspot candidates (shown in Figure 12(1)) has the shorter distance between wires at the corresponding area than the hotspot pattern, and the other (shown in Figure 12(2)) has the longer distance between wires at the corresponding area with the same difference. As mentioned above, the candidate with shorter distance is more likely to be a hotspot. However, these candidates have the same similarity (i.e., edit distance) to the hotspot pattern. In our extension, more critical hotspot candidates are found by considering the distance between wires and increasing the costs of the edit operations around the corresponding area (between wire segments with the minimum distance). Although there are vertical and horizontal distances, it is difficult to consider both the distances at the same time because our method is base on one-dimensional matching. Thus, we here discuss only horizontal distance between wires. Vertical distance can be handled in the same way.

The procedure is as follows. First, find the place where the distance between wires is the minimum in the hotspot pattern, by scanning the hotspot pattern. Then, calculate the threshold by multiplying the minimum distance and a userdefined coefficient. The threshold decides if the distance is short or not. Next, find the places where the distance between wires is less than or equal to the threshold in the hotspot pattern, by scanning the hotspot pattern again. We assume the places are likely to cause short circuits. Next, decrease the substitution costs of the places (between wires). If the places of the hotspot pattern are applied substitution operations, the non-wire pixels (= 0s) are substituted by wire pixels (= 1s). Thus, patterns more likely to be hotspots with shorter distance between wires can be found. The procedure is depicted in Figure 13.

#### IV. EXPERIMENTAL EVALUATION

We performed experiments to evaluate the effectiveness of our method. We evaluated the runtime of a two-dimensional template matching-based method and our one, and evaluated the hotspot candidates detected by ours. The two-dimensional template matching-based method is a method to detect hotspot candidates by matching the hotspot pattern and the mask pattern moving the hotspot pattern from the top-left corner to the bottom-left corner on the mask pattern pixel by pixel.

Figure 12. Hotspot pattern and its candidates

Figure 13. Detection of severe patterns

#### TABLE I. RUNTIME

|                 | Runtime (sec) |

|-----------------|---------------|

| 2D matching     | 152.02        |

| Non-LD method   | 906.54        |

| Proposed method | 512.41        |

In addition, we also evaluated the runtime of non-LD method which is based on our method but without large don't care characters, to evaluate the effectiveness of large don't care characters. The experiments are conducted on a Linux PC (CentOS release 6.3) equipped with Intel(R) Core(TM) i7-3770 CPU @ 3.40GHz CPU.

#### A. Comparison of Runtime

To evaluate runtime, we performed detection of hotspot candidates with a 1020x1020-pixel mask pattern and a 250x250-pixel hotspot pattern.

The runtime of each method is shown in Table I. The runtime of our method was longer than that of two-dimensional matching. However, we confirmed that large don't care characters improved the runtime.

Two-dimensional template matching starts its matching at the first column at the first row of the mask pattern, and moves to the next column until the right edge of the hotspot pattern reaches the right edge of the mask pattern. When the right edge of the hotspot pattern reaches the right edge of the mask pattern, it moves to the first column at the next row. This is repeated until the bottom-left corner of the hotspot pattern reaches that of the mask pattern. Thus, the time-complexity of two-dimensional matching is ((the width of the mask pattern) - (the width of the hotspot pattern))  $\times$  ((the height of the mask pattern) - (the height of the hotspot pattern))  $\times$  (the number of characters of the hotspot pattern)). On the other hand, the time-complexity of our proposed method is (the number of characters of the hotspot pattern)  $\times$  (the number of characters of the hotspot pattern)  $\times$  (the number of characters of the hotspot pattern)  $\times$  (the number of characters of the hotspot pattern)  $\times$  (the number of characters of the hotspot pattern)  $\times$  (the number of characters of the hotspot pattern)  $\times$  (the number of characters

Figure 15. Detected candidates

of the mask pattern). In addition, in the dynamic programming in our proposed method, three elements are referenced in the calculation of each element, and thus it takes time to calculate the value of an element compared to the case of template matching. They are the reasons why the runtime of our proposed method was longer than that of two-dimensional matching.

#### B. Comparison of Detected patterns

Original

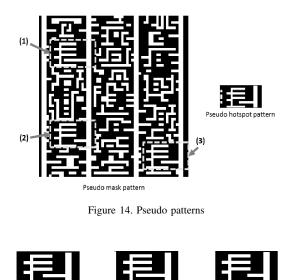

Next, we confirmed that if the detection of severe hotspot candidates considering the distances between wires is realized by our extension or not, using a pseudo mask pattern (60x60) and a pseudo hotspot pattern (10x20).

The standard cost of edit operations was set to 10, and the cost of each substitution operation at the places with distance between wires which is no more than the threshold was set to 5. The mask and hotspot patterns are shown in Figure 14, and the detected hotspot candidates are shown in Figure 15. The pattern (1) shown in Figure 15 is the same as the hotspot pattern, and thus their edit distance was 0. The edit distance of the pattern (2) is less than that of the pattern (3). As a result, the pattern (2) was detected in priority.

#### V. CONCLUSIONS

In this paper, we proposed a hotspot detection method based on approximate string search, and an extension which detects severe hotspot candidates in priority. Our future work includes more in-depth experiments using open benchmark data, comparison with other existing methods, analysis of patterns more likely to be hotspots, and extensions of our method based on the analysis.

#### REFERENCES

Tatsuhiko Higashiki and Yasunobu Onishi, "Trends in semiconductor lithography technologies and Toshiba's approach," TOSHIBA review, Vol.67, No.4, 2012, pp.2–6.

- [2] H. Yao, S. Sinha, J. Xu, C. Chiang, and X. Hong, "Efficient range pattern matching algorithm for process-hotspot detection," in Proc. IET Circuits Devices Syst., 2008, pp. 2–15.

- [3] D. Ding, A. J. Torres, F. G. Pikus, and D. Z. Pan, "High performance lithographic hotspot detection using hierarchically refined machine learning," in Proc. 16th Asia South-Pacific Design Autom. Conf. (ASP-DAC), Yokohama, Japan, 2011, pp. 775–780.

- [4] Jen-Yi Wuu, Fedor G. Pikus, and M. M-Sadowska, "Efficient approach to early detection of lithographic hotspots using machine learning systems and pattern matching," in Proc. SPIE 7974, Design for Manufacturability through Design-Process Integration V, 79740U, April 04, 2011.

- [5] S.-Y. Lin, J.-Y. Chen, J.-C. Li, W.-Y. Wen, and S.-C. Chang, "A novel fuzzy matching model for lithography hotspot detection," in Proc. Design Autom. Conf. (DAC), Austin, TX, USA, 2013, pp. 1–6.

- [6] W. Wen, J. Li, S. Lin, J. Chen, and S. Chang, "A fuzzy-matching model with grid reduction for lithography hotspot detection," IEEE Trans. on CAD, Vol. 33, No. 11, Nov. 2014, pp.1671–1679.

- [7] D. E. Knuth, J. H. Morris, Jr., and V. R. Pratt, "Fast pattern matching in strings," SIAM J. Comput., vol.6, no.2, 1977, pp.323–350.

- [8] Jhih-Rong Gao, Bei Yu, Duo Ding, and David Z. Pan, "Lithography Hotspot Detection and Mitigation in Nanometer VLSI," in Proc. IEEE International Conference on ASIC (ASICON), 2013, pp.1–4.

- [9] J. T. L. Ho and G. G. F. Lemieux, "PERG: A scalable FPGA-based pattern-matching engine with consolidated bloomier filters," in Proc. 2008 IEEE International Conference on Field Programmable Technology, Dec. 2008, pp.73–80.

- [10] Y. Sugawara, M. Inaba, and K. Hiraki, "Over 10Gbps string matching mechanism for multi-stream packet scanning system," in Proc. International Conference on Field Programmable Logic and Applications, Aug. 2004, pp.484–493.

- [11] B. C. Brogie, R. K. Cytron, and D. E. Taylor, "A scalable architecture for high throughput regularexpression pattern matching," in Proc. 33rd International Symposium on Computer Architecture, 2006, pp.191–202.

- [12] Yuichiro Utan, Shin'ichi Wakabayashi, and Shinobu Nagayama, "An FPGA-based text search engine for approximate regular expression matching," in Proc. International Conference on Field-Programmable Technology, Dec. 2010, pp.184–191.

- [13] Yuichiro Utan, Shin'ichi Wakabayashi, and Shinobu Nagayama, "A systolic algorithm for approximate regular expression matching and its FPGA implementation", IEICE Journal D, Vol. J94-D, No.6, June 2011, pp.935–944. (in Japanese)

- [14] Zhuo Li, et al., "ICCAD 2013 Contest," http://cadcontest.cs.nctu.edu.tw/CAD-contest-at-ICCAD2013/problem\_c/ [retrieved: June 2016].

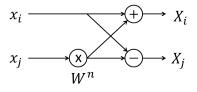

## Improving the Performance of a SOM-Based FPGA-Placement-Algorithm Using SIMD-Hardware

Timm Bostelmann and Sergei Sawitzki

FH Wedel (University of Applied Sciences) Wedel, Germany

Email: bos@fh-wedel.de, saw@fh-wedel.de

Abstract-Programmable circuits and nowadays especially fieldprogrammable gate arrays (FPGAs) are widely applied in demanding signal processing applications. In a previous work, we have introduced a method to improve the results of the netlistplacement for FPGAs with a self-organizing map (SOM). However, the presented algorithm conveys a comparably high computational effort. Considering modern, agile hardware/software codesign approaches, a slow design automation process can act as a kind of show-stopper, because software compilation is already distinctly faster. Thus, in this conceptual work, we present and evaluate different approaches to exploit the inherent parallelism of the SOM to increase the computation-speed. These approaches are based on using the single instruction multiple data (SIMD) capabilities of the central processing unit (CPU) and the graphics processing unit (GPU) for vector operations. Furthermore, we present benchmark results of an optimized implementation, based on using the CPU's SIMD units and introduce a concept for a GPU-accelerated implementation as work in progress.

Keywords–FPGA; netlist placement; GPU computing; parallelization; SIMD.

#### I. INTRODUCTION AND BACKGROUND

The ever-growing complexity of FPGAs has a high impact on the performance of electronic design automation (EDA) tools. A complete compilation from a hardware description language to a bitstream can take several hours. One step highly affected by the vast size of netlists is the NP-complete placement process. It consists of selecting a resource cell (position) on the FPGA for every cell of the applications netlist. Many current solutions optimize the placement iteratively. The academic EDA toolchain Verilog-to-Routing (VTR) Project for *FPGAs* [1] for example utilizes the simulated annealing [2] algorithm to solve the placement problem. Roughly described it starts with a random initial placement and applies random changes iteratively. The key of simulated annealing is the gradual reduction of the probability to keep disadvantageous changes over the time. Thereby the algorithm is able to leave local optima in early stages as well as to provide a fine optimization in later stages.

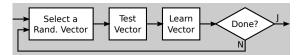

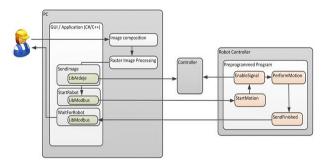

In [3], we have proposed a method to improve the placement results for FPGAs. Therefore, we have used a special SOM [4] to generate an initial placement optimized by a low temperature simulated annealing schedule. The placement generation consists of three stages (Figure 1). Initially for every cell of the netlist a training vector is generated. To guarantee that highly connected cells are represented by similar vectors, we use a hyperbolic distance function. The SOM is trained with these vectors in a random order. It consists of

Figure 1. Flowchart of the SOM-based placement algorithm.

Figure 2. Flowchart of the internal SOM training.